高压集成电路中的基准电压源 设计考量与实现策略

在高压集成电路的设计中,基准电压源扮演着至关重要的角色,它提供了一个与电源电压、工艺参数和温度变化无关的稳定参考电压,是模拟电路、电源管理以及数据转换器等模块正常工作的基石。随着集成电路向高压、高功率应用领域的拓展,如工业控制、汽车电子、医疗设备和显示驱动,对基准电压源的性能提出了更为严苛的要求。本文将探讨用于高压集成电路的基准电压源的设计原理、关键挑战以及主流实现方案。

一、 基准电压源的核心要求与高压设计挑战

一个理想的基准电压源应具备高精度、低温度系数、高电源抑制比以及良好的长期稳定性。在高压环境中,这些要求面临额外挑战:

- 高压兼容性:核心器件(如晶体管、电阻)必须能够承受远高于常规CMOS工艺(如3.3V或5V)的电压,通常需要数十伏甚至数百伏。这往往需要采用特殊的高压工艺(如BCD工艺)或器件结构(如LDMOS)。

- 功耗与面积:高压器件通常尺寸较大,且工作在高电压下,静态功耗和芯片面积的控制变得更为困难。

- 噪声与稳定性:高压电源本身可能引入更多噪声,且高压下的寄生效应(如漏电、热载流子效应)更显著,可能影响基准的长期稳定性和精度。

- 启动特性:在高压下,需要确保电路能够可靠、快速地启动,避免陷入不希望的稳定状态。

二、 主流设计架构

高压基准电压源的设计通常基于成熟的低压基准原理,但需要进行高压适应性改造。主要架构包括:

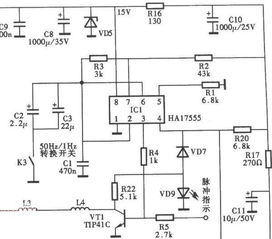

- 带隙基准电压源的拓展:

- 原理:利用双极型晶体管(BJT)基极-发射极电压(VBE)的负温度系数和热电压(VT=kT/q)的正温度系数相互补偿,产生一个近似零温度系数的基准电压(约1.25V)。

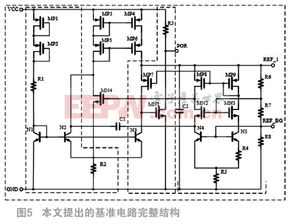

- 高压实现:在高压工艺中,BJT可能不可用或性能受限。常见的替代方案是使用高压MOSFET工作在亚阈值区来模拟BJT的指数特性,或者利用高压工艺中的寄生PNP/NPN晶体管。运算放大器(运放)和电流镜等辅助电路也必须采用高压器件实现。设计难点在于确保这些高压器件在宽电压范围内的匹配性和线性度。

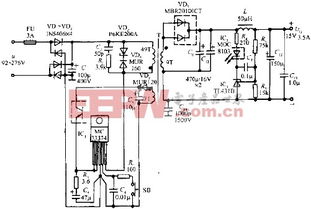

- 基于齐纳二极管的基准:

- 原理:利用齐纳二极管或雪崩二极管的击穿电压作为基准。其电压较高(通常>5V),且在一定电流范围内具有较好的稳定性。

- 高压实现:这种结构天然适合高压应用。设计关键在于提供一个精准、稳定的偏置电流源,并采取措施(如温度补偿电路、缓冲放大器)来改善其温度系数和输出阻抗。其缺点是噪声通常较大,功耗相对较高。

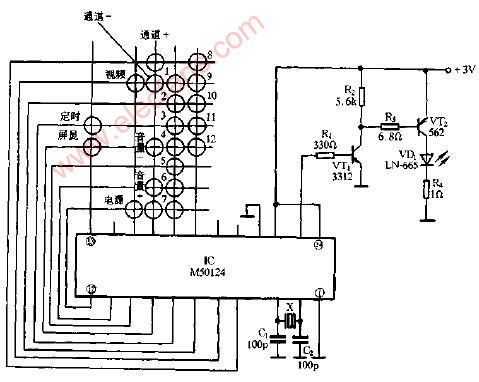

- 分压式基准:

- 原理:利用高精度电阻分压网络从高压电源中分出一个较低的参考电压。

- 高压实现:这是结构最简单的方案,但其精度直接受电源电压波动和电阻温度系数的影响,电源抑制比很差。通常需要与一个低压精密的带隙基准核心结合使用:首先由高压分压和稳压电路产生一个中间电压,再由此电压为低压带隙基准电路供电,最后输出一个高精度的低电压基准。这种分级结构能有效平衡性能和高压承受能力。

三、 关键设计技术与考量

- 启动电路:必须设计可靠的启动电路,确保在各种工艺角和温度下,基准核心能脱离零电流的简并点,进入正常工作状态。在高压下,启动电路本身也需具备高压耐受能力。

- 曲率补偿:基本的带隙基准输出电压随温度呈“碗形”曲线,存在高阶非线性误差。在要求极高的应用中,需要引入曲率补偿技术(例如利用不同电流密度下V_BE的差值)来进一步压低温度系数。

- 修调技术:由于工艺偏差,初始的基准电压可能存在偏移。片上集成修调电路(如激光熔丝、电可编程熔丝或非易失性存储器)可以在测试阶段对基准电压进行微调,以达到所需的精度。

- 布局与匹配:核心器件(如匹配的晶体管、电阻)的版图设计必须遵循严格的对称和共质心规则,以减小工艺梯度效应和热梯度效应引起的失配,这对精度至关重要。

- 电源抑制比增强:通过采用共源共栅电流镜、高增益运放反馈以及合理的电源去耦设计,可以显著提升基准电压对电源噪声的抑制能力。

四、 结论与展望

设计一种用于高压集成电路的基准电压源是一项多目标优化的工程。工程师必须在精度、温度稳定性、电源抑制比、功耗、面积以及高压可靠性之间做出权衡。目前,基于高压兼容的带隙基准架构和分级式(高压预处理+低压精调)架构是主流和可靠的选择。随着工艺的进步,未来可能出现集成度更高、性能更优、能直接工作在更高电压下的单片基准源解决方案。针对特定应用(如汽车级AEC-Q100标准)对高温、高可靠性的要求,基准源的设计也将更多地融入可靠性分析和鲁棒性设计理念。